– Mạch reset:

Chân reset là chân số 6. Bản thân bên trong chip đã có điện trở nối xuống GND.

Vì vậy nếu không cần thiết thì chân này có thể bỏ trống.

Nếu muốn mắc thêm nút nhấn Reset để khi ấn nút sẽ Reset chip thì có thể mắc song song 1 con tụ từ 5V tới chân Reset.

– Clock:

Chip sử dụng Dao động nội 24MHz, từ dao động nội này cung cấp xung cho bộ nhân tần số… Chip có thể sử dụng USB Full speed chỉ với mạch dao động nội. Khi không cấu hình gì thì chip sẽ sử dụng nguồn dao động nội 24MHz, tần số hệ thống Fsys = 6MHz.

Muốn cấu hình tần số Fsys thì thực hiện như sau:

+ Vào chế độ SAFE_MODE

* Gán SAFE_MOD = 0x55;

* Gán SAFE_MOD = 0xAA;

+ Ghi giá trị mới vào thanh ghi CLOCK_CFG

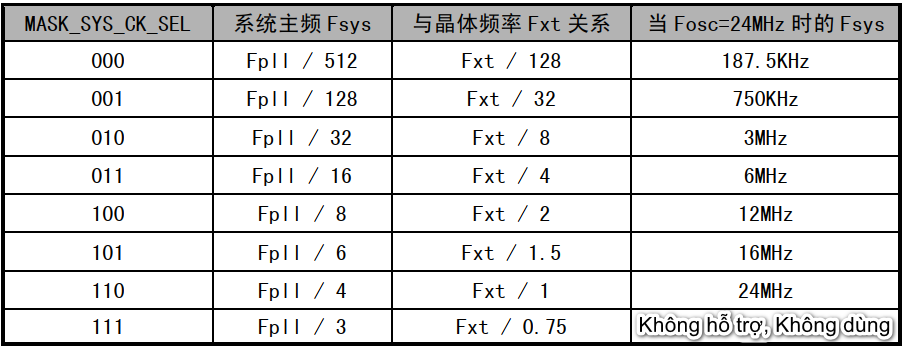

Giá trị MASK_SYS_CK_SEL quyết định tần số Fsys:

Thông thường sẽ cấu hình để Fsys đạt giá trị tối đa 24MHz nên gán MASK_SYS_CK_SEL = 0x06 vì vậy CLOCK_CFG = 0x86;

Quan hệ giữa MASK_SYS_CK_SEL và Fsys theo bảng

+ Ghi giá trị bất kì vào thanh ghi SAFE_MOD

* Gán SAFE_MOD = 0x00;

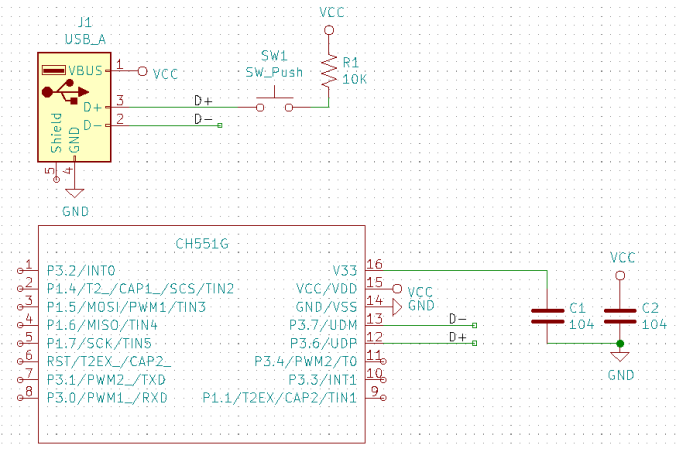

– Mạch điện tối thiểu:

Cần thêm 1 tụ 104 giữa VCC với GND.

Chân V33 cần thêm 1 tụ 104 nối với GND.

* Chân D+: khi cấp điện cho chip nếu chân này ở trạng thái 1 thì chip sẽ vào chế độ USB để có thể nạp chương trình. Khi không nối gì thì chân này sẽ ở trạng thái 0 và chip sẽ thực thi chương trình bình thường. Công tắc trong hình dùng để đưa chip vào chế độ nạp code, nếu công tắc được nhấn khi cấp nguồn thì chip vào chế độ nạp code.

Tham khảo mạch của KIT VĐK 1.0

http://vidieukhien.org/gioi-thieu-ve-kit-vdk-1-0.html